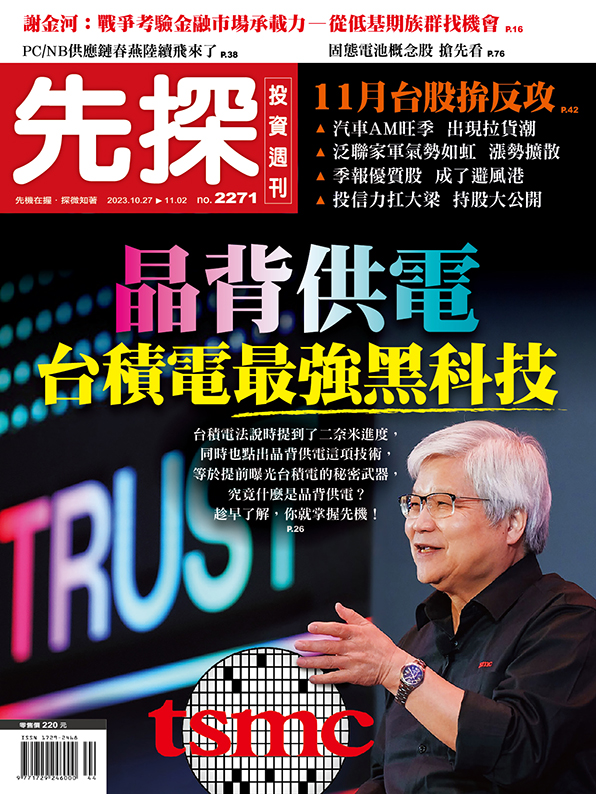

這回台積電法說會中,總裁魏哲家提到二奈米的開發進度,並簡單提到「晶背供電」技術,這個外界還不熟悉的神秘黑科技,就讓我們一探究竟!

【文/吳旻蓁】

晶圓代工龍頭廠台積電在十九日法說會上除了提及三奈米製程進度外,總裁魏哲家也透露觀察到二奈米在高速運算和智慧手機相關應用方面獲得客戶興趣和參與,與三奈米在同一階段時不相上下、甚至更高。而台積電預計二奈米將如期於二五年量產,且表示二奈米推出時,將是業界最先進的半導體技術;而適用於HPC的二奈米「背面電軌」(backside power rail)解決方案則預定二五年下半年推出、二六年量產。

台積電N2P將導入晶背供電

事實上,自二二年以來,台積電就多次發表二奈米晶片製程的研發進度;在今年的技術研討會上,台積電也表示N2P製程技術將通過晶背供電網路(BackSide Power Delivery Network; BSPDN)減少IR壓降(IR Drop)和改善信號,將性能提高十到十二%,並將邏輯面積減少十到十五%。

當前隨著電晶體逼近單奈米尺度,甚至比新冠病毒顆粒(約一二○奈米)還小,如何製作出更迷你、效能更高、能夠短時間量產的下一代元件,是半導體產業近年來一大棘手問題。也因此,晶片製造競爭持續白熱化,台積電、英特爾(Intel)、三星(Samsung)等晶片製造巨頭都在爭相展示三奈米、二奈米等先進工藝的技術突破,包括GAA(閘極全環電晶體)、High-NA(高數值孔徑)、先進封裝等一系列的創新技術,都是為了替摩爾定律續命。

而與EUV光刻機類似,晶背供電技術被視為繼續開發更精細工藝節點的關鍵技術,預期將成為晶片廠又一個新的競爭戰場。晶背供電技術的出現,為晶片製造帶來了一些全新的製程步驟。過去長久以來,晶片製造都是利用後段製程(BEOL),在矽晶圓的正面布線,透過這些低電組的導線來供應電力給晶片;也因為如此,晶片內的供電網路與訊號網路(即晶片內的訊號線)必須共用相同的元件空間。

但在製程節點持續推進之下,電晶體越來越小,密度越來越高,堆疊層數也越來越多,為了將電力從封裝傳輸至晶片中的晶體管,電子必須經由金屬導線和通孔,穿過十到二○層堆疊才能為下方電晶體提供電源和數據訊號。然而,越接近晶體管,線寬和通孔就越窄,電阻值也因而上升,使得電子在向下傳輸的過程中,會出現IR壓降現象,導致電力損失產生。

改變新一代邏輯晶片規則

除了電力損失,供電線路占用空間也是問題。晶片內的電源線路在布線複雜的後段製程上,往往占至少二○%的繞線資源,如何解決訊號網路跟供電網路之間的資源排擠問題,使元件進一步微縮,變成晶片設計者所面臨的主要挑戰之一。此外,電源線和接地線在標準單元設計上占了很大空間,使得組件很難進一步微縮。就系統設計而言,因為功率密度和IR壓降急遽增加,從穩壓器到晶體管的功率損失就很難控制在十%以下。對此,專家指出,如果不對晶片的電子進出方式進行大改變,無論製造多小的晶體管都無濟於事,也因此,業界開始研究將供電網路轉移到晶片背面的可能性。(全文未完)

全文及圖表請見《先探投資週刊2271精彩當期內文轉載》

◎封面故事:CoWoS設備廠訂單 很帶勁

◎特別企劃:季報優質股 將成避風港

◎國際趨勢:美股價值型投資 你也能當股神

◎中港直擊:歐美外商避中國唯恐不及

◎產業脈動:打上蘋果光 光學股默默漲

【最新活動看板】

◎先探i投資YouTube開播了

◎加入先探Telegram掌握第一手投資情報!

◎跟著生技女王腳步,奠定生技產業基本功

◎【先探講堂】廖鴻祿-新手存股輕鬆入門

◎【免費講座】贏賺創新財 台股大進擊

◎你沒有學到的資產配置!巴菲特的獲利秘密,你必須知道

◎訂先探送石墨烯枕,讓家人舒適健康好入眠